NVIDIA adopte des transistors GAA : Huang promet une augmentation de 20 % des performances

Lors de la conférence GTC 2025 à San Jose, le PDG de NVIDIA, Jensen Huang, a dévoilé des détails sur la stratégie technologique de l'entreprise, qui combine l'innovation en matière de semi-conducteurs avec le développement d'une infrastructure AI robuste. Selon Huang, la transition vers des transistors gate-all-around (GAA) dans les futurs puces Feynman — attendues d'ici 2028 — permettra d'augmenter les performances jusqu'à 20 %. Cependant, l'entreprise met l'accent sur des solutions architecturales et logicielles plutôt que de se précipiter pour adopter les derniers procédés de fabrication.

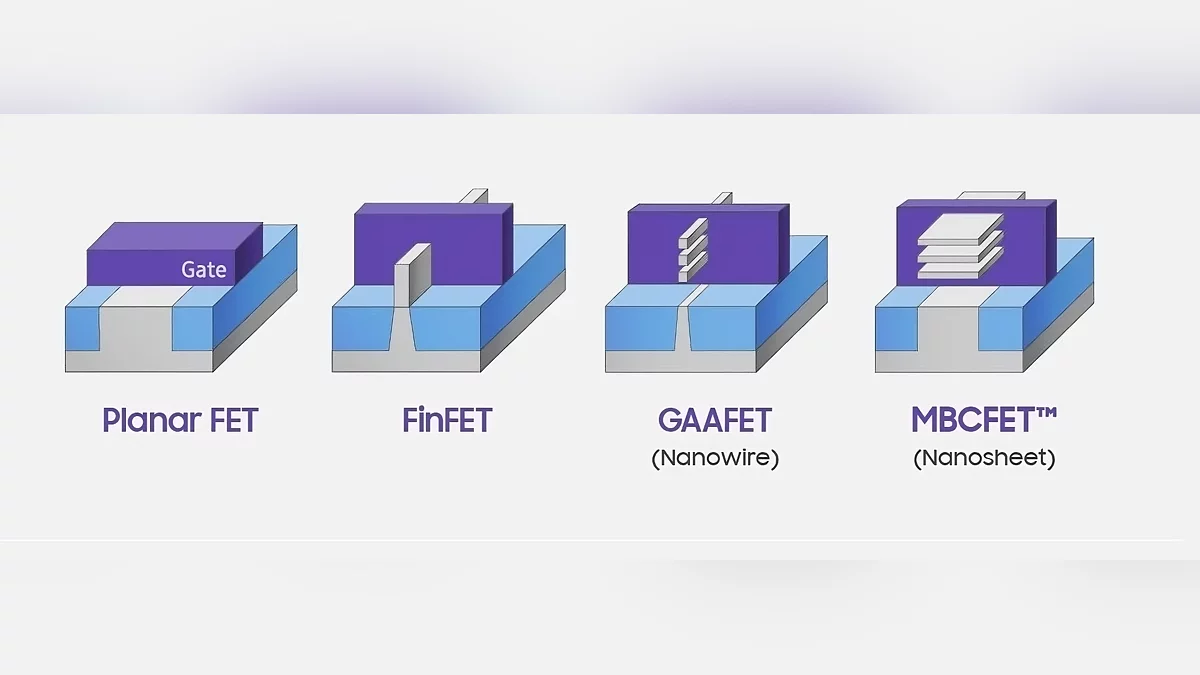

Huang a noté que l'ère des percées révolutionnaires en lithographie touche à sa fin. Même le passage aux nœuds prometteurs de 2 nm avec des transistors GAA, comme l'estime TSMC, devrait n'offrir qu'une amélioration de 10 à 15 % des performances. Néanmoins, NVIDIA — traditionnellement prudente vis-à-vis des technologies « brutes » — prévoit d'utiliser des versions optimisées telles que N2P ou A16 avec une alimentation inversée. Huang pense que cette approche permettra d'atteindre le gain de 20 % revendiqué en réduisant la résistance et en stabilisant la consommation d'énergie.

Huang a clairement déclaré que NVIDIA ne se considère plus comme un fabricant traditionnel de semi-conducteurs. Au lieu de cela, l'entreprise construit une infrastructure AI complète qui englobe des algorithmes pour la vision par ordinateur, la robotique et même la conception de puces. Un exemple de cette stratégie est les futures plateformes Rubin (prévue pour 2026) sur le processus N3P de 3 nm, qui intégrera le GPU Vera et un CPU dans une architecture unifiée pour les centres de données. Pourtant, comme le souligne Huang, leur plein potentiel ne sera réalisé que lorsqu'ils seront combinés avec des frameworks propriétaires comme CUDA et Omniverse.

Le buzz autour de la technologie GAA est bien fondé, car ces transistors sont effectivement capables d'offrir un gain de performance. Dans les transistors GAA, la porte entoure complètement le canal conducteur, minimisant les fuites et améliorant le contrôle. Les analystes notent que les déclarations de Huang reflètent une tendance plus large dans l'industrie : déplacer l'accent de l'augmentation des vitesses d'horloge vers l'optimisation de l'efficacité énergétique et de l'évolutivité. Avec l'expansion des clusters AI, même un gain de 20 % au niveau des puces pourrait potentiellement doubler les performances des centres de données — à condition que l'intégration soit gérée intelligemment.

-

Rumeur : NVIDIA prévoit de lancer deux versions de GeForce RTX 5060 Ti en avril

-

NVIDIA dévoile la série de cartes graphiques RTX PRO 6000 avec 96 Go de mémoire

-

NVIDIA dévoile un PC avec un processeur à 72 cœurs et un GPU Blackwell

-

NVIDIA Défend l'Échec de l'RTX 50, Blâme les Utilisateurs

-

NVIDIA publie une mise à jour pour l'application NVIDIA avec personnalisation DLSS